In a groundbreaking study conducted by scientists from Tokyo Tech, two novel design techniques were found to significantly enhance the performance of fractional-N phase locked loops (PLLs). The primary focus of these methods was to reduce fractional spurs, which are unwanted signals that commonly affect PLLs in various radar systems and wireless transceivers. These advancements have the potential to revolutionize technologies such as wireless communication, autonomous vehicles, surveillance, and tracking systems in the post-5G era.

Wireless data transceivers, radar systems, self-driving vehicles, tracking systems, and remote sensors heavily rely on the accurate and high-speed operation of phase locked loops (PLLs). PLLs play a crucial role in synthesizing, modulating, and synchronizing oscillating signals, making them indispensable components in numerous applications. Therefore, the reduction or elimination of errors in PLLs is vital for enhancing the overall performance of these systems.

Fractional-N PLLs, a popular type of PLL known for its exceptional resolution and versatile frequency control, often face challenges such as jitter and fractional spurs. Jitter refers to the deviation from the ideal timing of oscillation, while fractional spurs are unwanted signals that result from errors in the system. Digital-to-time converters (DTCs) are typically utilized in digital PLLs to mitigate quantization errors. However, imperfections in DTCs, particularly integral non-linearities (INLs), contribute to the generation of fractional spurs, which degrade the phase noise in PLL outputs.

The research team led by Professor Kenichi Okada from Tokyo Institute of Technology developed two innovative design techniques to address the challenges faced by fractional-N PLLs. The first technique involved the utilization of a cascaded-fractional divider. By splitting the frequency control word (FCW) into two values that are not close to an integer, the researchers aimed to introduce fractional spurs at higher frequencies that are naturally filtered by the PLL. This approach was designed to minimize complexity and delay compared to conventional methods involving digital pre-distortion (DPD).

The second technique focused on the implementation of a pseudo-differential DTC to overcome the limitations of standard DTC designs. By recognizing the even symmetric components in the non-linearities of DTCs, the researchers utilized two half-range DTCs with identical even-symmetric INLs to perform differential operations. This setup allowed for the cancellation of INLs through subtraction at the PLL’s phase detector, leading to improved performance in reducing fractional spurs.

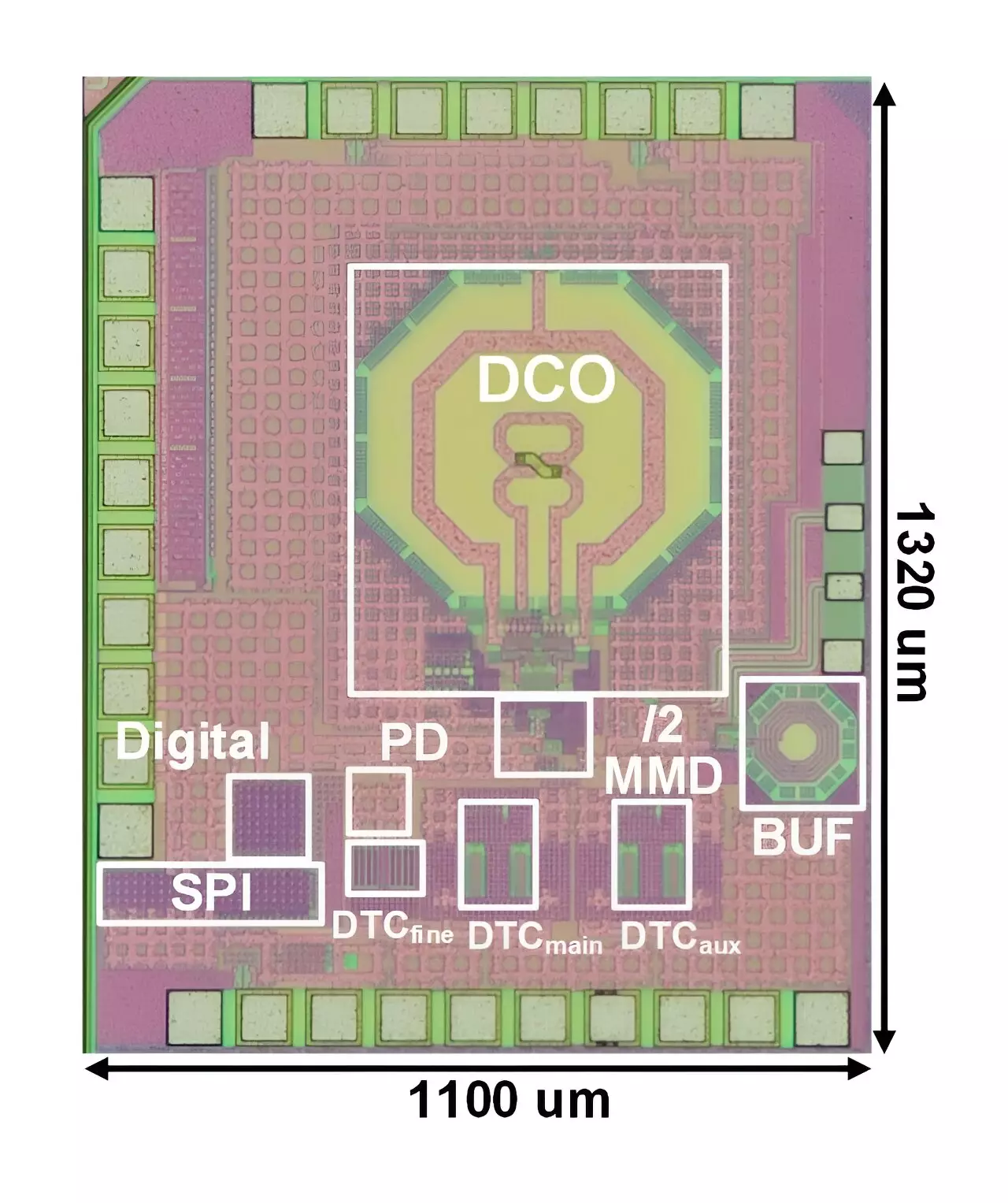

To validate their concepts, the research team implemented the proposed digital PLL using a 65 nm CMOS process, requiring a minimal active circuit area of 0.23 mm2. Comparative analysis with state-of-the-art designs showed significant improvements in performance. By effectively suppressing fractional spurs, the integrated PLL jitter was reduced from 243.5 fs to 143.7 fs. Professor Okada highlighted that the innovative cascaded fractional divider and pseudo-differential DTC techniques enabled achieving the lowest class of jitter without the need for DPD technology.

The introduction of these innovative design techniques for fractional-N PLLs represents a significant milestone in improving the performance and reliability of wireless communication, radar systems, autonomous vehicles, surveillance, and tracking technologies. The successful implementation of the cascaded fractional divider and pseudo-differential DTC methods has the potential to drive technological advancements across various applications where fractional-N PLLs are prevalent.

Leave a Reply